Journal of Futuristic Sciences and Applications Vol. 5(1), Jan-Jun 2022, pp. 11-21 doi: 10.51976/jfsa.512202 www.gla.ac.in/journals/jfsa © 2022 JFSA, GLA University

# Using Power Reduction Techniques, a Comparison of Differential and Latch Type Sense Amplifier Circuits

Dharmendra Kumar Tiwari\*, Narendra Kumar Verma\*\* and Jitendra Singh Kirar\*\*\*

#### **ABSTRACT**

Researchers have investigated several different sense amplifiers' yield and other quantitative features. Amplification is required for various power-saving methods, including the sleep transistor, the sleep stack, the sleepy keeper, and others. This study aims to evaluate how much energy is consumed by the many different sense amplifier topologies. Simulations have shown that adopting a sleep transistor approach can significantly reduce the amount of power lost even while operating at 1.2V.

**Keywords:** SRAMC (Static Random-Access Memory Cell); VMDSA (voltage mode differential sense amplifier); Sense Amplifier (SA); VLSA (voltage latch sense amplifier); CLSA (current latch sense amplifier).

#### 1.0 Introduction

The development of smaller transistors has led to increased VLSI density and efficiency of devices [1]. Wires are used to link the transistors that make up an integrated circuit. Time and power are exchanged between semiconductors over worldwide networks. Many VLSI applications, such as the buses that link cache memory to CPUs, rely on global communication latency as VLSI technology develops to submicron scales. This is because submicron sizes are required for VLSI technology. [2] With more time passing, the four-way latency of this worldwide semiconductor connectivity will get worse. More than one type of signal transmission may be utilized thanks to several transceivers, which connect the various channels via which signals can be conveyed. As the use of battery-powered computers becomes more widespread, new low-energy storage options are being developed. Because of the leakage current, the number of transistors in the SRAMC system has risen, turning it into a block that requires a lot of power. SRAM blocks have a huge impact on the architecture of modern SoCs and how they are designed.

Utilizing sensing amplifiers, data is often accessible from static random-access memory cells (SRAMC) and dynamic random-access memory (DRAM) (DRAM). Data of high quality may tolerate many different types of noise while still faithfully portraying the information in a memory cell. They find that even moderate levels of noise are intolerable at times. Several circuits require

<sup>\*</sup>Corresponding author; PhD Scholar, Department of Mechanical Engineering, United University, Prayagraj, Mathura, Uttar Pradesh, India (E-mail: dharmu.tiwari@gmail.com)

<sup>\*\*</sup>Madhav Institute of Technology & Science, Gwalior, Madhya Pradesh, India (Email: narendra.verma@itmgoi.in)

<sup>\*\*\*</sup>Department of Mechanical Engineering, RGPV (Rajiv Gandhi Prodyogiki Vishwavidyalaya, State Technical University), Bhopal, Madhya Pradesh, India

quick sensing amplifiers to cut down on the amount of time spent waiting. There is a significant amount of memory that makes use of bit lines. Interconnection is becoming an increasingly essential factor in developing sub-micrometer CMOS devices to reduce the amount of delay that occurs on-chip. Possibly, high-speed sensing amplifiers are required for large-chip high-speed signal repeaters [3-5]. The market for battery-powered mobile devices and embedded systems is expanding, and this growth is occurring concurrently with the expansion of the VLSI (large-scale integrated circuit) sector. Cache memory information can take up as much as sixty to seventy percent of the chip's surface area. When additional chips are used, the speed of the CPU slows down [6-8]. Businesses are looking at the possibility of developing a low-speed, low-power memory circuit to keep up with the ever-increasing expansion of VLSI systems. Individual chip failure rates are affected by adding or removing one million transistors at a time. The sensory amplifier is the main topic of this article (SA). It is now the case that high-performance microprocessors employ more than half of their transistors for cache memory, and it is anticipated that this percentage will continue to rise in the future [9–12]. Because the SRAMC in these chips operates effectively even when significant external sounds are present, the built-in stock is usually utilized. Consequently, more people started investing in developing computers that consume less power. If the device has the appropriate SRAMCs, it can store the memory it requires. A city can progress rapidly if it is well planned and efficiently managed. Memory blocks of the SRAMC wouldn't exist if it weren't for the SA, which can detect high frequencies. The configuration of the sensing amplifier determines the amount of time and energy required to access the memory. Memory devices' peripheral circuitry largely relies on SA for their operation. [13-16] Power-operated SA can decrease the gap between memory cells and the arbitrary logic levels of Boolean circuits by converting signals from bits to digital logical levels. This is accomplished by converting the signals. Memory loss and the amount of time it takes to recover are significantly influenced by the rate at which these structures expand. For CMOS memory to compete with conventional integrated circuits, it must expand faster, be more robust, and consume less power. The SA memory will not be useful to us in achieving these objectives. A common occurrence is an increase in the amount of parasite space used by the bit line concurrently with the expansion of the total memory capacity of the system. This bit line has been expanding [17–20] as the use of memory that requires a lot of energy has gotten increasingly widespread.

#### 2.0 Power Reduction Techniques

This section discusses low power reduction strategies used in amplifiers such as the VMDSA, CMDSA, CLSA, and CLSA.

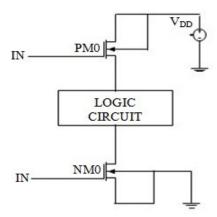

#### 2.1 Sleep transistor technique

For this treatment, most people employ sleep transistors [21]. Figure 1 shows that the pull-up network is connected to both the VDD and the GND.

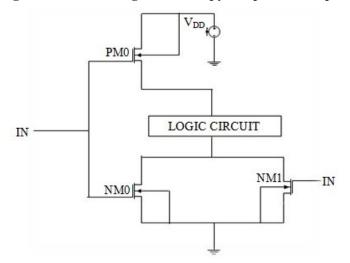

## 2.2 Sleepy-keeper technique

A mattress that can be folded into a bed by stringing together PMOS transistors in series between the pull-up network and VDD and the pull-down network and GND, this technique employs NMOS and PMOS transistors builds a circuit. This method makes it simpler to control outflow wells without modifying the operation of a small field circuit. While the device is in sleep mode, an

NMOS transistor connected to VDD and a pull-up network is activated. This guarantees that the value of the data is always "1." A PMOS transistor is wired with both the pull-down network and GND. Doing this maintains the data's value of "0". As seen in Figure. 2 [22], a "0" data value is maintained by turning on a second PMOS transistor.

Figure 1: Circuit Diagram of Sleep Transistor Technique

Figure 2: Circuit Diagram of Sleepy Keeper Technique

#### 3.0 Sense Amplifiers

The sensing amplifier is a crucial element in terms of memory. Sense amplifiers (SAs) have developed into a distinct class of semiconductor memory circuits due to their quick evolution [23-27]. Since sensing does not damage the circuits, it is not necessary to feed the circuits with new data after sensing. Sensory amplifiers must almost always fulfill the following requirements:

#### 3.1 Differential type sense amplifier

The circuit for the MOS sense amplifier has every element needed for differential sensing. Background noise can be reduced while real-world signal discrepancies can be increased. Since amplification uses so much energy and goes slowly, it cannot serve as a memory [28].

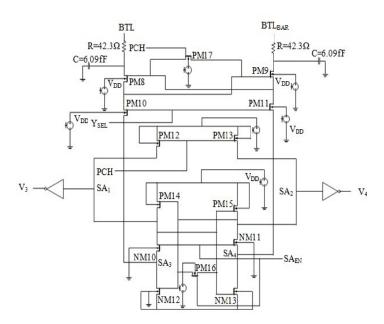

## 3.1.1 Voltage mode differential sense amplifier

A short MOS differential voltage sense amplifier circuit with all the elements needed for differential sensing is shown in Figure 3.

BTL BTL R=42.3Ω C=6.09fF

PM10 PM11 PCH

PM12 PM12 PM14 VDD

SA<sub>EN</sub> NM12 NM11 SA<sub>EN</sub> NM12 PM14 VDD

SA<sub>EN</sub> NM14 VDD

SA<sub>EN</sub> NM15 PM14 VDD

SA<sub>EN</sub> NM15 PM

Figure 3: Schematic of Voltage Mode Differential Sense Amplifier

A differential amplifier's output must only have one end. The value of a differential amplifier depends on its capacity to amplify the difference between two real signals while ignoring background noise. Simple differential voltage amplification is not used in memory due to its slow working speed, high power consumption, and the large offset [29, 30].

## 3.1.2 Current mode differential sense amplifier

Figure 4: Schematic of Current Mode Differential Sense Amplifier

Differential current detection is used to find the difference between the input and output of the current-carrying amplifier. The anticipated use of the CMDSA is shown in Figure 4. Four Pmos transistors are used to enhance the signal (PM8-PM9-PM10-PM11). When utilizing a Pmos, similar latching and delay timings are applied to internal nodes SA1 and SA2 [31-34].

## 3.2 Latch type sense amplifier

Two inverters are used in the six-transistor SRAMC architecture to provide a sensing amplifier. The latch-type SA is preloaded and positioned in the high-gain metastable zone to start sensing [35]. If the latch-type SA is too close to the bit-lines, a "0" bit-line will be left empty; as a result, the latch-type SA must be kept away from the bit-lines.

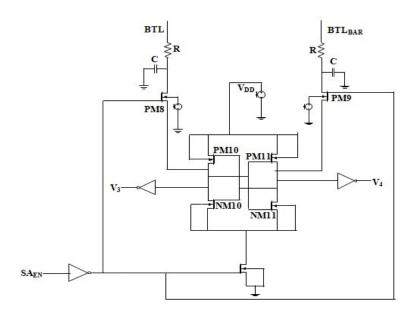

# 3.2.1 Voltage latch sense amplifier

Figure 5 shows the designs for the voltage latching sensing amplifiers. The nodes in this system are pre-charged using bit-lines. Bit lines are immediately moved to internal nodes of a circuit being built [36-38].

Figure 5: Schematic of Voltage Latch Sense Amplifier

The PM8 and PM9 pass transistors turn on as soon as the WL is raised. The permissible internal nodes of a sensing amplifier increase with the distance between two-bit lines. Every time the inverters PM10, NM10, PM11, and NM11 send the sensor signal SAen, the differential voltage grows until it reaches its maximum swing output.

### 3.2.2 Current latch sense amplifier

The SA is a circuit that creates cache memory. The voltage supply to each bit remains constant throughout the reading, even when one-bit line drains and the other. There is a sign of a current lock on the amplifier in Figure 6.

The discharge delay is caused by the large bit-line capacitance and the small access transistor. In this stage, SA transforms an analog signal into a digital signal [39,40]. The bit lines' voltage differential is sent into the CLSA's SA3 and SA4 inputs. The SA1 and SA2 outputs will discharge if the SAEN pull-up resistor is cranked high. NM12 can receive more current because it has higher Vgs than NM13. Because of this, V3 uses up its energy reserves faster than V4.

PM8 PM9

PM10 PM11

PM12

PM13 PM14

PM15

SA<sub>PCH</sub>

SA<sub>PCH</sub>

V<sub>3</sub>

NM10 NM11

NM11

NM12

NM14

Figure 6: Schematic of Current Latch Sense Amplifier

# 4.0 Comparison Table

The power requirements of several sense amplifiers are covered in this article, both with and without power-saving techniques.

| Sense Amplifiers | Power Consumption |  |

|------------------|-------------------|--|

| VMDSA            | 90.95μW           |  |

| CMDSA            | 60.23μW           |  |

| VLSA             | 500.78μW          |  |

| CLSA             | 200.58μW          |  |

**Table 1: Power Consumption of Sense Amplifier**

VMDSA experiences the least amount of power loss of any SA, as seen in Table 1. Table 2 also demonstrates that when low-power techniques like sleep transistors are used, CMDSA consumes the least power.

**Table 2: Power Reduction Techniques over Sense Amplifiers**

| Techniques Used  | Power Consumption |        |          |         |

|------------------|-------------------|--------|----------|---------|

|                  | VMDSA             | CMDSA  | VLSA     | CLSA    |

| Footer Stack     | 60.24μW           | 0.62μW | 320.88μW | 99.58μW |

| Sleep Transistor | 60.54μW           | 0.61µW | 310.54μW | 70.92μW |

| Sleepy -Keeper   | 60.85μW           | 0.60μW | 340.21μW | 98.57μW |

#### 5.0 Conclusion

It was discovered that latch sense amplifiers and current-mode and voltage differential sense amplifiers were used in the study. There were also used other kinds of sensors. The sleep transistor, sleep stack, sleepy keeper, and sleep stack use sensing amplifiers to minimize power usage. The least electricity is used with sleep transistor technology using current mode differential sensing.

#### References

- 1. Yong-peng Tao, Wei-ping Hu, "Design of Sense Amplifier in the High-Speed SRAM," International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery, pp. 384-387, 2015.

- 2. Menu Rani Garg, Anu Tonk, "A Study of Different Types of Voltage & Current Sense Amplifier used in SRAM," International Journal in Advanced Research in Computer and Communication Engineering, Vol.4, PP: 30-35.

- 3. Aiyappan Natarajan, Vijay Shanker, Atul Maheshwari, "Sensing Design Issue in Deep Submicron CMOS SRAM," IEEE Computer Society Annual Symposium on VLSI, pp- 42-45, 2005.

- 4. Kamal Pandey, Vishal Yaday, "Design and Analysis of Low Power Latch Sense Amplifier," IOSR Journal of Electronics and Communication Engineering, Vol.9, PP: 69-73, 2014.

- 5. .Geetha Priya, Dr.K.Baskaran, D.Krishnaveni. "Leakage Power Reduction Techniques in Deep Submicron Technologies for VLSI Applications" ELSEVIER, International Conference on Communication Technology and System Design 2011.

- 6. Afshin Abdollahi, Farzan Fallah, Massoud Pedram, "A Robust Power Gating Structure and Power Mode Transition Strategy for MTCMOS Design," Very Large Scale Integration (VLSI) Systems IEEE Transactions on, vol. 15, pp. 80-89, 2007, ISSN 1063-8210

- 7. A. Sathanur, A. Pullini, L. Benini, A. Macii, E. Macii, M. Poncino, "A Scalable Algorithmic Framework for Row-Based Power-Gating," Design Automation and Test in Europe 2008. DATE '08, pp. 379-384, 2008, ISSN 1530-1591

- 8. K Sridhara, G S Biradar, Raju Yanamshetti, "Subthreshold leakage power reduction in VLSI circuits: A survey," Communication and Signal Processing (ICCSP) 2016 International Conference on, pp. 1120-1124, 2016.

- 9. H. Dounavi, Y. Sfikas, and Y. Tsiatouhas, "Periodic Aging Monitoring in SRAM Sense Amplifiers," 2018 IEEE 24th International Symposium on On-Line Testing And Robust System Design (IOLTS), Platja d'Aro, 2018, pp. 12-16.

- 10. Na, S. Woo, J. Kim, H. Jeong, and S. Jung, "Comparative Study of Various Latch-Type Sense Amplifiers," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 2, pp. 425-429, Feb. 2014.

- 11. Manoj Sinha, Steven Hsu, Atila Alvandpour, Wayne Burleson, Ram Krishnamurthy, Shekhar Borhr. "High-Performance and Low-Voltage Sense-Amplifier Techniques for sub-90nm SRAM." SOC Conference, 2003. Proceedings. IEEE International [Systems-on-Chip].

- 12. Baker Mohammad, Percy Dadabhoy, Ken Lin, Paul Bassett. "Comparative study of current mode and voltage mode sense amplifier used for 28nm SRAM." 24th International Conference on Microelectronic, 07 March 2013.

- 13. Yiqi Wang, Fazhao Zhao, Mengxin Liu, and Zhengsheng Han, "A new full current-mode sense amplifier with compensation circuit," 2011 9th IEEE International Conference on ASIC, Xiamen, 2011, pp. 645-648.

- 14. Ravi Dutt, Abhijeet. "High-Speed Current Mode Sense Amplifier for SRAM Applications." IOSR Journal of Engineering, Vol. 2, pp. 1124-1127, 2012

- 15. Zikui Wei, Xiaohong Peng, JinhuiWang, Haibin Yin, Na Gong, "Novel CMOS SRAM Voltage Latched Sense Amplifiers Design Based on 65nm Technology" PP: 3281-3282.

- 16. D. Arora, A. K. Gundu and M. S. Hashmi, "A high-speed, low voltage latch type sense amplifier for non-volatile memory," 2016 20th International Symposium on VLSI Design and Test (VDAT), Guwahati, 2016, pp. 1-5.

- 17. Reeya Agrawal, V. K. Tomar. "Analysis of Cache (SRAM) Memory for Core I <sup>TM</sup> 7 Processor",9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), 2018,402.

- D. Schinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time," 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, 2007, pp. 314-605.

- V. M. Tripathi, S. Mishra, J. Saikia, and A. Dandapat, "A Low-Voltage 13T Latch-Type Sense Amplifier with Regenerative Feedback for Ultra Speed Memory Access," 2017 30th International Conference on VLSI Design and 2017 16th International Conference on Embedded Systems (VLSID), Hyderabad, 2017, pp. 341-346.

- 20. A. Hemaprabha and K. Vivek, "Comparative analysis of sense amplifiers for memories," 2015 International Conference on Innovations in Information, Embedded and Communication Systems (ICIIECS), Coimbatore, 2015, pp. 1-6.

- 21. M. Jefremow et al., "Time-differential sense amplifier for sub-80mV bit line voltage embedded STT-MRAM in 40nm CMOS," 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, 2013, pp. 216-217.

- 22. Y. Tao and W. Hu, "Design of Sense Amplifier in the High-Speed SRAM," 2015 International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery, Xi'an, 2015, pp. 384-387.

- 23. Rajendra Prasad S, BK Madhavi, K Lal Kishore, "design of 32nm Forced Stack CNTFET SRAM Cell for Leakage Power Reduction", IEEE Conference on Computing, Electronics and Electrical Technologies, pp. 629-633, 2012.

- 24. A. Sathanur, A. Pullini, L. Benini, A. Macii, E. Macii, M. Poncino, "A Scalable Algorithmic Framework for Row-Based Power-Gating," Design Automation and Test in Europe 2008. DATE '08, pp. 379-384, 2008, ISSN 1530-1591.

- 25. J. K. Mishra, H. Srivastava, P. K. Misra, and M. Goswami, "A 40nm Low Power High Stable SRAM Cell Using Separate Read Port and Sleep Transistor Methodology," 2018 IEEE International Symposium on Smart Electronic Systems (iSES) (Formerly iNiS), Hyderabad, India, 2018, pp. 1-5.

- 26. Tarunnum Sultana, S.Jagadesh, M.Naveen Kumar, "A Novel Dual-Stack Sleep Technique for Reactivation Noise Suppression in MTCMOS Circuits," IOSR Journal of VLSI and Signal Processing, Vol.-3, pp.32-37, 2013.

- 27. K.Gnana Deepika, K.Mariya Priyadarshini, K. David Solomon Raj. "Sleepy Keeper Approach for Power Performance Tuning in VLSI Design." International Journal of Electronics and Communication Engineering. ISSN 0974-2166 Volume 6, Number 1(2013), pp.17-28.

- 28. Chakka Sri Harsha Kaushik, Rajiv Reddy Vanjarlapati, Varada Murali Krishna, Tadavarthi Gautam, V Elamaran, "VLSI design of low power SRAM architectures for FPGAs," Green Computing Communication and Electrical Engineering (ICGCCEE) 2014 International Conference on, pp. 1-4, 2014.

- 29. Richa Choudhary, Srinivasa Padhy, NirmalKumar Rout, "Enhanced Robust Architecture of Single Bit SRAM Cell using Drowsy Cache and Super cut-off CMOS Concept," International Journal of Industrial Electronics and Electrical Engineering, Volume-3, PP.63-68, July 2011.

- 30. Jesal P. Gajjar, Aesha S. Zala, Sandeep K. Aggarwal, "Design and Analysis of 32 bit SRAM architecture in 90nm CMOS Technology" Volume: 03, Issue: 04, Apr-2016, pp:2729-2733.

- 31. Reeya Agrawal, V. K. Tomar. "Analysis of Cache (SRAM) Memory for Core I TM 7 Processor",9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), 2018,40225.

- 32. Kundan Vanama, Rithwik Gunnuthula, Govind Prasad, "Design of low power stable SRAM cell," Circuit Power and Computing Technologies (ICCPCT) 2014 International Conference on, pp. 1263-1267, 2014.

- 33. Shikha Saun, Hemant Kumar, "Design and performance analysis of 6T SRAM cell on different CMOS technologies with stability characterization", OP Conf. Series: Materials Science and Engineering 561 (2019) 012093.

- 34. A. Bhaskar, "Design and analysis of low power SRAM cells," 2017 Innovations in Power and Advanced Computing Technologies (i-PACT), Vellore, 2017, pp. 1-5.

- 35. Yong-peng Tao, Wei-ping Hu, "Design of Sense Amplifier in the High-Speed SRAM," International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery, pp. 384-387, 2015.

- 36. M. Jefremow et al., "Time-differential sense amplifier for sub-80mV bit line voltage embedded STT-MRAM in 40nm CMOS," 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, 2013, pp. 216-217.

- 37. Y. Tao and W. Hu, "Design of Sense Amplifier in the High-Speed SRAM," 2015 International Conference on Cyber-Enabled Distributed Computing and Knowledge Discovery, Xi'an, 2015, pp. 384-387.

- 38. Yiqi Wang, Fazhao Zhao, Mengxin Liu, and Zhengsheng Han, "A new full current-mode sense amplifier with compensation circuit," 2011 9th IEEE International Conference on ASIC, Xiamen, 2011, pp. 645-648.

- 39. T. Na, S. Woo, J. Kim, H. Jeong, and S. Jung, "Comparative Study of Various Latch-Type Sense Amplifiers," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 22, no. 2, pp. 425-429, Feb. 2014.

- 40. Yiping Zhang, Ziou Wang, Canyan Zhu, Lijun Zhang, Aiming Ji, and Lingfeng Mao, "28nm latch type sense amplifier coupling effect analysis," 2016 International Symposium on Integrated Circuits (ISIC), Singapore, 2016, pp. 1-4.

- 41. Parashar, A. K., Sharma, P., & Sharma, N. (2022). An investigation on properties of concrete with the adding of waste of ceramic and micro silica. Materials Today: Proceedings.

- 42. Sharma, N., Sharma, P., & Parashar, A. K. (2022). Use of waste glass and demolished brick as coarse aggregate in production of sustainable concrete. Materials Today: Proceedings.

- 43. A review on the mechanical properties of polymer composites reinforced by carbon nanotubes and graphene, A Kumar, K Sharma, AR Dixit, Carbon Letters, 1-17

- 44. Effect of functionalized graphene/CNT ratio on the synergetic enhancement of mechanical and thermal properties of epoxy hybrid composite, MK Shukla, K Sharma, Materials Research Express 6 (8), 085318

- 45. Investigating the effects of amine functionalized graphene on the mechanical properties of epoxy nanocomposites, A Yadav, A Kumar, K Sharma, MK Shukla, Materials Today: Proceedings 11, 837-842

- 46. N. Sharma, P. Sharma, and S. kr Verma, "Influence of Diatomite on the properties of mortar and concrete: A Review," in IOP Conference Series: Materials Science and Engineering, 2021, vol. 1116, no. 1, p. 12174.

- 47. N. Sharma and P. Sharma, "Effect of hydrophobic agent in cement and concrete: A Review," IOP Conference Series: Materials Science and Engineering, vol. 1116, no. 1, p. 012175, 2021, doi: 10.1088/1757-899x/1116/1/012175.