Journal of Futuristic Sciences and Applications Vol. 3(1), Jan-Jun 2020, pp. 57-63 doi: 10.51976/jfsa.312008 www.gla.ac.in/journals/jfsa © 2020 JFSA, GLA University

# Single Bit Architecture Low Power Cache Memory Design Analysis

Tarun Sikarwar\* and Anurag Shrivastava\*\*

### ABSTRACT

This paper examines voltage latch sensing amplifiers and six-transistor static RAM cells. The single-bit architecture's cache memory design has been investigated at various resistance values. Utilizing Process Corner Simulation and Monte Carlo Simulation, the stability of the design was evaluated. A single-bit static random access memory cell latch sensing amplifier architecture uses less energy as the resistance value rises.

*Keywords:* Voltage Latch Sense Amplifier (VLSA); Write Driver Circuit (WDC); Latch Sense Amplifier (LSA); Six Transistors Static Random-Access Memory (STSRAM).

#### **1.0 Introduction**

The three primary types of computer memory in use today are basic memory, cache memory, and register data [1-3]. Large-scale integrated circuits, or STSRAM technology, are frequently used by businesses to speed up procedures. Structured random-access memory (SRAM), a crucial memory component for processing data, typically makes up cache memory. This is an important factor to consider while considering STSRAM's potential growth. Even when the power is down, STSTRAM enables anyone with physical access to the device to view the data [4-7]. Due to its connection to the data line in a STSRAM, the LSA is frequently disregarded. LSA monitors the voltage on each bit line, and the total voltage swing as each bit line is read. Swing voltage cannot be used to record or measure data. It will store "0" or "1" in place of "0" or "1." As the VLSI industry grows, embedded systems and battery-powered mobile devices are taking on more significance [8-10]. Cache memory takes up between 60 and 70 per cent of the chip's area in a singlebit architecture. When the number of chips in use rises quickly, CPU speed falls [8-10]. The business world is creating a low-speed, low-power memory circuit to keep up with VLSI's developments. A million transistors can alter a single device's failure rate. It is anticipated that cache memory in highperformance microprocessors will increase until it uses more than half the transistors. Due to its great dependability and stability, STSRAM is frequently used for on-chip storage in noisy situations. Since all SRAMC cells are the same size, the system can use any of them. It is common practice to estimate a system's time and power requirements using the LSA setup [11-14].

## 2.0 Design of Cache Memory for Single Bit Architecture

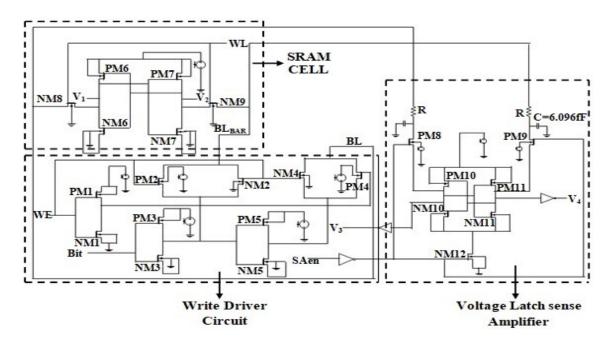

Here, designers discussed the cache memory's single-bit design in Figure 1. WDC, STSRAM, and LSA are workable solutions in a single-bit cache memory architecture.

<sup>\*</sup>Corresponding author; Director, DKT Technology Services Pvt. Ltd., (E-mail: tarun.sikarwar@dkt.co.in) \*\*Assistant Professor, Department of Mechanical Engineering, SR Institute of Management and Technology, Lucknow, Uttar Pradesh, India. (E-mail: onuda@rediffmail.com)

58 Journal of Futuristic Sciences and Applications, Volume 3, Issue 1, Jan-Jun 2020 Doi: 10.51976/jfsa.312008

Figure 1: Design of Cache Memory for Single Bit Architecture

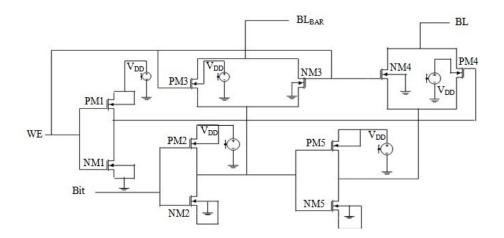

### 2.1 Circuit of write driver

It is dependable and a great option for tasks needing low voltage and power. A two-way latch is used to store each bit in a circuit [15,16]. Figure 5 depicts the NM3 and NM4 driving transistors for a STSRAM cell. One of the transistors in this circuit is the driving transistor. These bit lines widen the noise margin. Researchers can calculate how much voltage can fluctuate by using a differential circuit. As long as the present power cycle lasts, the logical state won't change. The DRAMC should not be refilled at this time [17]. When creating a STSRAM, the transistor's size is crucial.

### Figure 2: Write Driver Circuit Schematic

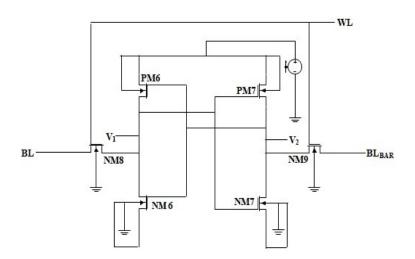

#### 2.2 Six transistor static random-access memory cell

It's perfect for jobs that don't call for a lot of power or voltage. A circuit that can latch in both directions is used to store each bit. The STSRAM cell in Figure 3 has two pull-ups, two drivers, and two pull-downs [18-20]. These bit lines widen the noise margin. A differential circuit can be used to

compute the voltage swings that can be measured. The logical state of this power cycle is either 0 or 1. The DRAMC does not, however, need to be changed as a result of this. When designing a STSRAM, the size of the transistors is crucial [21].

Figure 3: Six Transistor Static Random Access Memory Cell Schematic

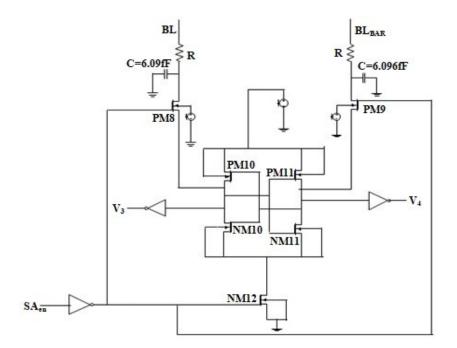

### 2.3 Voltage latch sense amplifier

Figure 4 depicts the schematics for the voltage latch detecting amplifier in this instance. In this design, the nodes are charged in advance via bit-lines. The circuit's building blocks, the nodes, manage the input bit lines. When the word line is lifted, the amplifier sensor fires, but PM8 and PM9 are not engaged. The voltage differential impacts the random bit voltage in the internal nodes of the LSA between the bit lines. When the LSA SAEN signal is claimed, the greater voltage difference between inverters boosts maximum swing power [22–25].

#### Figure 4: Schematics of Voltage Latch Sense Amplifier

60 Journal of Futuristic Sciences and Applications, Volume 3, Issue 1, Jan-Jun 2020 Doi: 10.51976/jfsa.312008

#### 3.0 Result Analysis

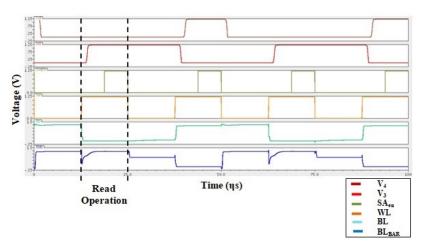

Figure 5 depicts a simulation of the cache memory using a single-bit design.

Figure 5: Output Waveform of VLSA

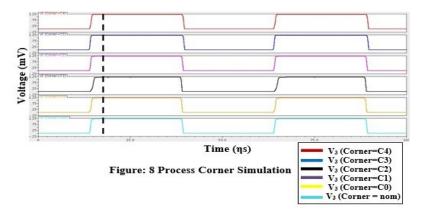

Figure 6 displays the outcomes of a Monte Carlo simulation of the cache memory setup for a single-bit architecture.

**Figure 6: Process Corner Simulation**

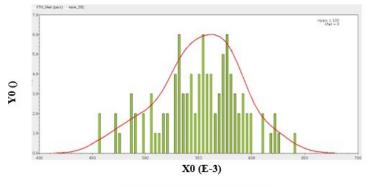

**Figure 7: Monte Carlo Simulation**

Figure: 9 Monte Carlo Simulation

Table: 1 shows that when resistance increases, power consumption falls.

| S.No. | Parameters | Delay in Sensing | Number of<br>Transistors | Consumption of<br>Power |

|-------|------------|------------------|--------------------------|-------------------------|

| 1.    | R=42.3Ω    | 25.78ηs          | 30                       | 40.21µW                 |

| 2.    | R=42.3KΩ   | 25.78ŋs          | 30                       | 20.89µW                 |

### Table 1: Analysis of Single Bit SRAMC VLSA Design's Different Parameters

#### 4.0 Conclusion

The different resistance levels of the single-bit cache memory structure are used to investigate these architectural elements. Monte Carlo and corner simulation have also been used to analyze the cache memory design for a single-bit architectural process. According to a study, single-bit cache memory consumes more power as resistance rises. In the future, this work might benefit from the use of arrays.

### References

- Y. He, J. Zhang, X. Wu, X. Si, S. Zhen, and B. Zhang, "A Half-Select Disturb-Free 11T SRAM Cell with Built-In Write/Read-Assist Scheme for Ultralow-Voltage Operations," in IEEE Transactions on Very Large-Scale Integration (VLSI) Systems, vol. 27, no. 10, pp. 2344-2353, Oct. 2019.

- R. Fragasse et al., "Analysis of SRAM Enhancements Through Sense Amplifier Capacitive Offset Correction and Replica Self-Timing," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 6, pp. 2037-2050, June 2019.

- S. Gupta, K. Gupta, B. H. Calhoun, and N. Pandey, "Low-Power Near-Threshold 10T SRAM Bit Cells with Enhanced Data-Independent Read Port Leakage for Array Augmentation in 32nm CMOS," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 3, pp. 978-988, March 2019.

- H. Dounavi, Y. Sfikas, and Y. Tsiatouhas, "Periodic Aging Monitoring in SRAM Sense Amplifiers," 2018 IEEE 24th International Symposium on On-Line Testing and Robust System Design (IOLTS), Platja d'Aro, 2018, pp. 12-16.

- S. Ahmad, B. Iqbal, N. Alam, and M. Hasan, "Low Leakage Fully Half-Select-Free Robust SRAM Cells with BTI Reliability Analysis," in IEEE Transactions on Device and Materials Reliability, vol. 18, no. 3, pp. 337-349, Sept. 2018.

- B. N. K. Reddy, K. Sarangam, T. Veeraiah, and R. Cheruku, "SRAM cell with better read and write stability with Minimum area," TENCON 2019 - 2019 IEEE Region 10 Conference (TENCON), Kochi, India, 2019, pp. 2164-2167.

- 62 Journal of Futuristic Sciences and Applications, Volume 3, Issue 1, Jan-Jun 2020 Doi: 10.51976/jfsa.312008

- A. Surkar and V. Agarwal, "Delay and Power Analysis of Current and Voltage Sense Amplifiers for SRAM at 180nm Technology," 2019 3rd International Conference on Electronics, Communication, and Aerospace Technology (ICECA), Coimbatore, India, 2019, pp. 1371-1376.

- Tripathi Tripti, Chauhan D. S., Singh S. K., and Singh S. V. "Implementation of Low-Power 6T SRAM Cell Using MTCMOS Technique", In Advances in Computer and Computational Sciences, Springer, Singapore, 2017.

- 9. M.Geetha Priya, Dr.K.Baskaran, D.Krishnaveni. "Leakage Power Reduction Techniques in Deep Submicron Technologies for VLSI Applications." ELSEVIER, International Conference on Communication Technology and System Design 2011.

- K Sridhara, G S Biradar, Raju Yanamshetti, "Subthreshold leakage power reduction in VLSI circuits: A survey," Communication and Signal Processing (ICCSP) 2016 International Conference on, pp. 1120-1124, 2016.

- 11. K.Gnana Deepika, K.Mariya Priyadarshini, K. David Solomon Raj. "Sleepy Keeper Approach for Power Performance Tuning in VLSI Design" International Journal of Electronics and Communication Engineering.ISSN 0974-2166 Volume 6, Number 1(2013), pp.17-28.

- 12. Gomes Iuri A.C., Meinhardt Cristina, Butzen Paulo F. "Design of 16nm SRAM Architecture" South Symposium on Microelectronics, 2012.

- Chakka Sri Harsha Kaushik, Rajiv Reddy Vanjarlapati, Varada Murali Krishna, Tadavarthi Gautam, V Elamaran, "VLSI design of low power SRAM architectures for FPGAs," Green Computing Communication and Electrical Engineering (ICGCCEE) 2014 International Conference on, pp. 1-4, 2014.

- Richa Choudhary, Srinivasa Padhy, Nirmal Kumar Rout, "Enhanced Robust Architecture of Single Bit SRAM Cell using Drowsy Cache and Super cut-off CMOS Concept," International Journal of Industrial Electronics and Electrical Engineering, Volume-3, PP.63-68, July 2011.

- 15. Jesal P. Gajjar, Aesha S. Zala, Sandeep K. Aggarwal, "Design and Analysis of 32-bit SRAM architecture in 90nm CMOS Technology" Volume: 03, Issue: 04, Apr-2016, pp:2729-2733.

- 16. Reeya Agrawal, V. K. Tomar. "Analysis of Cache (SRAM) Memory for Core I <sup>™</sup> 7 Processor",9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), 2018,402.

- 17. Kundan Vanama, Rithwik Gunnuthula, Govind Prasad, "Design of low power stable SRAM cell," Circuit Power and Computing Technologies (ICCPCT) 2014 International Conference on, pp. 1263-1267, 2014.

- Rakesh Dayaramji Chandankhede, Debiprasad Priyabrata Acharya, Pradip Kumar Patra, "Design of High-Speed sense Amplifier for SRAM," IEEE International Conference on Advanced Communication Control and Computing Technologies, pp. 340-343.

- 19. Zikui Wei, Xiaohong Peng, JinhuiWang, Haibin Yin, Na Gong, "Novel CMOS SRAM Voltage Latched Sense Amplifiers Design Based on 65nm Technology" pp.3281-3282.

- 20. Yiqi Wang, Fazhao Zhao, Mengxin Liu, and Zhengsheng Han, "A new full current-mode sense amplifier with compensation circuit," 2011 9th IEEE International Conference on ASIC, Xiamen, 2011, pp. 645-648.

- 21. Singh, S., Mishra, V. Enhanced Static Noise Margin and Increased Stability SRAM Cell with Emerging Device Memristor at 45-nm Technology 61, 200–206 (2018).

- 22. Saxena, K. K., Srivastava, V., & Sharma, K. (2012). Calculation of Fundamental Mechanical Properties of Single Walled Carbon Nanotube Using Non-Local Elasticity. Advanced Materials Research, 383–390, 3840–3844. https://doi.org/10.4028/WWW.SCIENTIFIC.NET/ AMR.383-390.3840