Journal of Futuristic Sciences and Applications Vol. 5(1), Jan-Jun 2022, pp. 48-55 doi: 10.51976/jfsa.512207 www.gla.ac.in/journals/jfsa © 2022 JFSA, GLA University

# Single-Bit Architecture Cache Memory Design Analysis

Abhishek Srivastava\*, Shashank Saxena\*\* and Tarun Sikarwar\*\*\*

#### **ABSTRACT**

This work includes the design of voltage and current difference latches and low-power cache memory for a single-bit processor core architecture. To save power, the single-bit cache memory uses voltage differential sensing amplifiers.

**Keywords:** Voltage differential sense amplifier (VDSA); Write Driver Circuit (WDC); Current Latch Sense Amplifier (CLSA); Differential Sense Amplifier (DSA); Six Transistors Static Random-Access Memory (STSRAM); Latch Sense Amplifier (SA).

#### 1.0 Introduction

Many mobile gadgets and systems that work together demand batteries [1]. The single-bit cache memory on the chip, which takes up 60 to 70 per cent of its surface area, is where the data is kept. As chip utilization rises, CPU speed declines. As demand for VLSI systems increases quickly, low-speed, low-power memory circuits are designed to keep up. The number of transistors added or subtracted impacts how quickly a chip fails for each. The fundamental premise of the paper is that sensory stimulation improves cognition. According to predictions, memory cache will eventually occupy more than half of high-performance microprocessor transistors [2]. SRAMC semiconductors are renowned for functioning effectively in noisy situations. Due to this, high-performance computers with lower electrical requirements have become more popular. With SRAMC, smaller memory cells are not a concern. This means the user can utilize the entire amount of RAM on the gadget. A city grows and evolves more quickly and drastically than other areas. There is a SA, which is sensitive to high frequencies, inside each SRAMC memory block. SA typically takes into account things like memory access times and power consumption. In memory systems, side circuits [3,4] play a key role. By digitizing the analogue levels in peripheral Boolean networks, the SA can hasten data transmission from one memory cell to the next in the logic circuit [5].

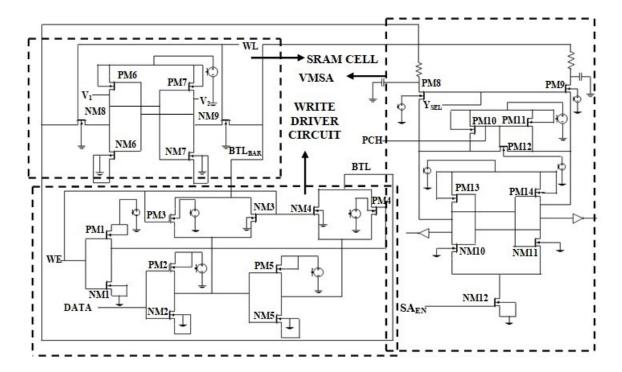

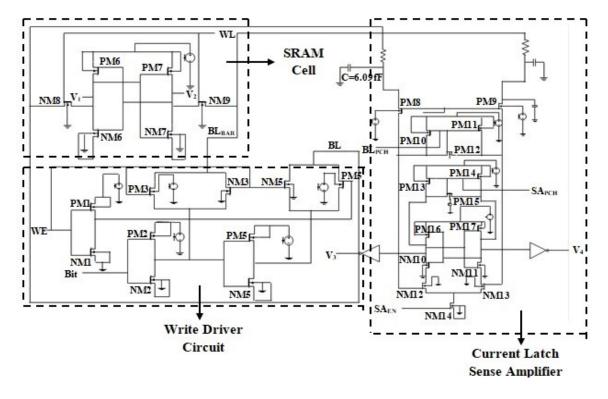

# 1.1 Single bit architecture cache memory design

This section covered the operation of single-bit cache memory. The concept is only partially illustrated in Figures. 1 and 2. The Cache Memory Design for Single-Bit Architecture includes WDC, STSRAM, and other sense amplifiers, including voltage differential and current latch sense amplifiers [11,12].

<sup>\*</sup>Corresponding author; Assistant Professor, Department of Mechanical Engineering, SR Institute of Management and Technology, Lucknow, Uttar Pradesh, India (E-mail: sriabhi1991@gmail.com)

<sup>\*\*</sup>Assistant Professor, Department of Mechanical Engineering, Bansal Institute of Science and Technology, Bhopal, Madhya Pradesh, India (E-mail: shashanksaxena7oct@gmail.com)

<sup>\*\*\*</sup>Director, DKT Technology Services Pvt. Ltd. (E-mail: tarun.sikarwar@dkt.co.in)

Figure 1: Single Bit STSRAM VDSA Architecture

Figure 2: Single Bit STSRAM CLSA Architecture

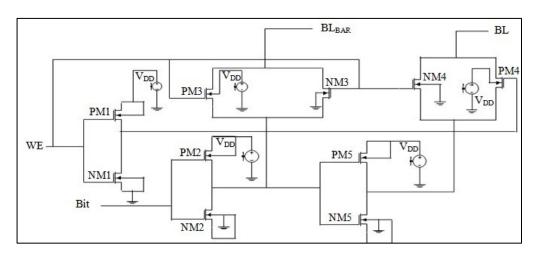

## 1.2 WDC

The WDC is seen in action in Figure 3. The STSRAM write driver quickly drains each bit line from the pre-charge stages once the write margin has been achieved.

Figure 3: WDC

The write enables (WE) signal, which activates the write data converter, is typically sent over the bit line. A pre-charge takes place before the full-swing charge to the ground (WDC). Every PMOS and NMOS in the WDC's stock are now in use. Every PMOS has a PMOS for PM1, PM2, PM3, PM4, and PM5 (NM1, NM2, NM3, NM4, and NM5). Depending on the data, one of the transistors may be PM1 or NM1.

### **1.3 SRAMC**

It works well for tasks that don't require much power or voltage. A latching circuit tracks each bit. Driving (M1 and M2) and drawing up transistors are shown in Figure 4. (PMOS). There is more noise margin with these bit lines. It is unnecessary to reload DRAM cells [15, 16] while the power is still on. The performance of an SRAM is influenced by transistor size.

BL PM6

PM7

V1

V2

NM8

NM9

BLBAR

Figure 4: SRAMC

### 1.4 DSA and LSA

The sensing amplifier causes the voltage differential between the read-access bit lines to increase. The overall quality of the digital output depends on the amplification. More transistors are necessary to break up lengthy data lines. The metal is stronger as a result.

### **1.5 VMSA**

The amplifier receives power from the voltage difference between the two-bit lines. A crossconnected inverter converts the initial voltage difference between the bit lines into full swing output. The cell column bit lines multiply the BTL and BTLBAR inputs. The sensory boost, which also activates the memory cell in P1 and the sensory boost in P2, is triggered by N3. To shield the internal nodes of the sensor amplifier from outside influences, output inverters are necessary [17,18].

BTLBAR BTL ≷R=42.3Ω R=42.3Ω ≷ C=6.09fF C=6.09fF PM9 PMS PM10 PM11 PCH PM12 PM14 PM13 NM10 NM11 NM12

Figure 5: VMSA

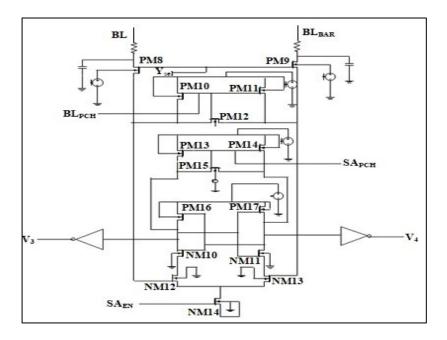

# **1.6 CLSA**

Figure 6: CMSA

The internal structure of a current latching amplifier is shown in Figure 6. The circuit is covered in great detail in [19, 20]. The CLSA's SA3 and SA4 observe the voltage variations on the bit lines. SA1 and SA2 emerge each time SAEN ascends. A positive feedback loop is established when the sensing amplifier's level is low enough to activate the PMOS device PM16. SA2 splits its inputs and outputs to lessen chargeback interference.

# 2.0 Results Analysis

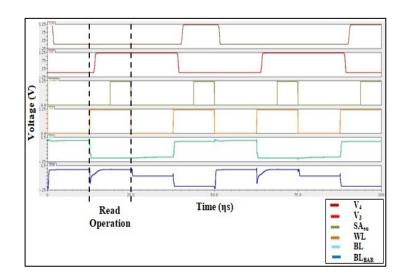

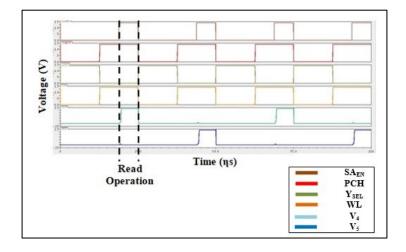

The SAEN and WL are both high in Figures 7 and 8, even though the VDSA and CLSA are in reading mode. Only V3 and V4 can access STSRAM data while the SA is present.

Figure 7: VMSA O/P

Figure 8: Current Latch Sense Amplifier Output Waveform

Table 1 shows that the power consumption of single-bit STSRAM VDSA devices decreases when resistance increases. The cache memory in Table 2 uses a single-bit STSRAM CLSA design, which uses less power.

Table 1: Different Cache Memory Design Parameters are Employed for Single Bit STSRAM VDSA Architecture

| Parameters | Single Bit STSRAM VDSA Architecture |                      |

|------------|-------------------------------------|----------------------|

|            | Delay in Sensing                    | Consumption of Power |

| R=42.3Ω    | 25.25ηs                             | 13.16μW              |

| R=42.3KΩ   | 25.25ηs                             | 11.34µW              |

Table 2: Design considerations for Single Bit STSRAM CLSA **Architecture Cache Memory**

| Parameters - | Single Bit STSRAM CLSA Architecture |                      |

|--------------|-------------------------------------|----------------------|

|              | Delay in Sensing                    | Consumption of Power |

| R=42.3Ω      | 25.25ηs                             | 81.78μW              |

| R=42.3KΩ     | 25.25ηs                             | 30.12μW              |

#### 3.0 Conclusion

It is feasible to enhance the cache memory properties of voltage differential sense amplifiers and current latch sense amplifiers by increasing the resistance (R) in the design. The number of transistors, the amount of power consumed, and the sensor's response time. One strategy for cutting power usage is to use single-bit memory blocks. A voltage differential sensing amplifier and a static random access memory cell with six transistors are used to create a single-bit cache memory.

### References

- Eslami, N., Ebrahimi, B., Shakouri, E. et al. A single-ended low leakage and low voltage 10T 1. SRAM cell with high yield. Analog Integr Circ Sig Process 105, 263–274 (2020).

- 2. Bazzi, H., Harb, A., Aziza, H. et al. RRAM-based non-volatile SRAM cell architectures for ultra-low-power applications. Analog Integr Circ Sig Process (2020).

- 3. S. Gupta, K. Gupta, B. H. Calhoun, and N. Pandey, "Low-Power Near-Threshold 10T SRAM Bit Cells With Enhanced Data-Independent Read Port Leakage for Array Augmentation in 32-nm CMOS," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 3, pp. 978-988, March 2019.

- 4. H. Dounavi, Y. Sfikas, and Y. Tsiatouhas, "Periodic Aging Monitoring in SRAM Sense Amplifiers," 2018 IEEE 24th International Symposium on On-Line Testing And Robust System Design (IOLTS), Platja d'Aro, 2018, pp. 12-16.

- 5. S. Ahmad, B. Iqbal, N. Alam, and M. Hasan, "Low Leakage Fully Half-Select-Free Robust SRAM Cells With BTI Reliability Analysis," in IEEE Transactions on Device and Materials Reliability, vol. 18, no. 3, pp. 337-349, Sept. 2018.

- 6. B. N. K. Reddy, K. Sarangam, T. Veeraiah, and R. Cheruku, "SRAM cell with better read and write stability with Minimum area," TENCON 2019 2019 IEEE Region 10 Conference (TENCON), Kochi, India, 2019, pp. 2164-2167.

- 7. Tripathi Tripti, Chauhan D. S., Singh S. K., and Singh S. V. "Implementation of Low-Power 6T SRAM Cell Using MTCMOS Technique", In Advances in Computer and Computational Sciences, Springer, Singapore, 2017.

- 8. M.Geetha Priya, Dr K.Baskaran, D.Krishnaveni "Leakage Power Reduction Techniques in Deep Submicron Technologies for VLSI Applications" ELSEVIER, International Conference on Communication Technology and System Design 2011.

- 9. K Sridhara, G S Biradar, Raju Yanamshetti, "Subthreshold leakage power reduction in VLSI circuits: A survey," Communication and Signal Processing (ICCSP) 2016 International Conference on, pp. 1120-1124, 2016.

- 10. Gomes Iuri A.C., Meinhardt Cristina, Butzen Paulo F. "Design of 16nm SRAM Architecture" South Symposium on Microelectronics, 2012.

- 11. Chakka Sri Harsha Kaushik, Rajiv Reddy Vanjarlapati, Varada Murali Krishna, Tadavarthi Gautam, V Elamaran, "VLSI design of low power SRAM architectures for FPGAs," Green Computing Communication and Electrical Engineering (ICGCCEE) 2014 International Conference on, pp. 1-4, 2014.

- 12. Richa Choudhary, Srinivasa Padhy, Nirmal Kumar Rout, "Enhanced Robust Architecture of Single Bit SRAM Cell using Drowsy Cache and Super cut-off CMOS Concept," International Journal of Industrial Electronics and Electrical Engineering, Volume-3, PP.63-68, July 2011.

- 13. Jesal P. Gajjar, Aesha S. Zala, Sandeep K. Aggarwal, "Design and Analysis of 32 bit SRAM architecture in 90nm CMOS Technology" Volume: 03, Issue: 04, Apr-2016, pp:2729-2733.

- 14. Reeya Agrawal, V. K. Tomar "Analysis of Cache (SRAM) Memory for Core I <sup>TM</sup> 7 Processor", 9th International Conference on Computing, Communication and Networking Technologies (ICCCNT), 2018,402.

- 15. Kundan Vanama, Rithwik Gunnuthula, Govind Prasad, "Design of low power stable SRAM cell," Circuit Power and Computing Technologies (ICCPCT) 2014 International Conference on, pp. 1263-1267, 2014.

- 16. Rakesh Dayaramji Chandankhede, Debiprasad Priyabrata Acharya, Pradip Kumar Patra, "Design of High-Speed sense Amplifier for SRAM," IEEE International Conference on Advanced Communication Control and Computing Technologies, pp. 340-343, 2016

- 17. Zikui Wei, Xiaohong Peng, JinhuiWang, Haibin Yin, Na Gong, "Novel CMOS SRAM Voltage Latched Sense Amplifiers Design Based on 65nm Technology" pp.3281-3282, 2016.

- 18. B. Wicht, T. Nirschl, and D. Schmitt-Landsiedel, "Yield and speed optimization of a latchtype voltage sense amplifier," in the IEEE Journal of Solid-State Circuits, vol. 39, no. 7, pp. 1148-1158, July 2004.

- 19. T. Kobayashi, K. Nogami, T. Shirotori, Y. Fujimoto and O. Watanabe, "A current-mode latch sense amplifier and a static power-saving input buffer for low-power architecture," 1992 Symposium on VLSI Circuits Digest of Technical Papers, Seattle, WA, USA, 1992, pp. 28-29.

- 20. T. Kobayashi, K. Nogami, T. Shirotori, and Y. Fujimoto, "A current-controlled latch sense amplifier and a static power-saving input buffer for low-power architecture," in IEEE Journal of Solid-State Circuits, vol. 28, no. 4, pp. 523-527, April 1993.

- 21. Sharma, N., Sharma, P., & Parashar, A. K. (2022). Use of waste glass and demolished brick as coarse aggregate in production of sustainable concrete. Materials Today: Proceedings.

- 22. Sharma, P., Sharma, N., & Parashar, A. K. (2022). Effects of phase-change materials on concrete pavements. Materials Today: Proceedings.