**Article Info**

Received: 25 Jul 2017 | Revised Submission: 20 Aug 2017 | Accepted: 28 Aug 2017 | Available Online: 15 Dec 2017

# Single OTRA based Low Voltage Square Root Circuit

Gaurav Aggarwal\*, Harsh Garg\*\*, Nishank Bansal\*\*\*, Pranav Gangwar\*\*\*\* and Rajeshwari Pandey\*\*\*\*

# ABSTRACT

This paper presents an analog square root circuit using single Operational Transresistance Amplifier (OTRA). It can be used to obtain the square root of the low input voltage. This circuit does not use any external passive component and hence is suitable for integration. The proposed circuit is verified with the help of simulations using  $0.18\mu m$  CMOS parameters on PSPICE. The theoretical observations are in accordance with the simulation result.

Keywords: Analog Square Root Circuit; OTRA; Low Voltage.

### **1.0 Introduction**

Analog square root circuit is used extensively in measurement [1], low voltage analog multiplier [2] and operational trans-conductanceamplifier [3]. Many circuits have been proposed for implementation of square root circuit [4-5].

This square root circuit has been implemented using operational transsistance amplifier. OTRA has gained immense popularity in recent times.

It is used as an alternate active block for implementation of analog circuits [6-7] since it inherits all the advantages of current mode techniques.

It is a three-terminal current input voltage output device. The input is free from parasitic capacitances and resistances since the input terminals are virtually grounded internally.

OTRA has been implemented using CMOS in various forms in the literature [7]. This paper presents a low voltage analog square root circuit which is suitable for integration.

### 1.2 Proposed square root circuit

### **1.3 OTRA**

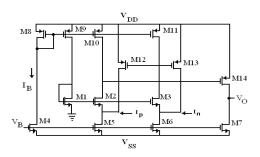

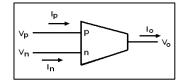

OTRA is a Current Controlled Voltage Amplifier and its V-I relationship can be defined by the following matrix where  $R_m$  is the transresistance gain of OTRA.Ideally  $R_m$  is infinite which forces input currents to be equal. Hence negative feedback is employed in OTRA. The CMOS based implementation of OTRA is shown in Fig. 1 and its circuit symbol is depicted in Fig. 2.

$$\begin{bmatrix} V_P \\ V_n \\ V_o \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ R_m & -R_m & 0 \end{bmatrix} \begin{bmatrix} I_P \\ I_n \\ I_o \end{bmatrix} \qquad \dots (1)$$

### Fig 1: OTRA Schematic [8]

<sup>\*</sup>Department of Electronics and Communication Engineering, Delhi Technological University New Delhi – 110042, India \*\*Department of Electronics and Communication Engineering, Delhi Technological University New Delhi – 110042, India \*\*\*\*Department of Electronics and Communication Engineering, Delhi Technological University New Delhi – 110042, India (E-mail: nishankbansal\_2k14ec103@dtu.ac.in)

<sup>\*\*\*\*</sup>Department of Electronics and Communication Engineering, Delhi Technological University New Delhi – 110042, India (E-mail: pranavgangwar\_2k14ec116@dtu.ac.in)

<sup>\*\*\*\*\*</sup> Corresponding Author: Department of Electronics and Communication Engineering, Delhi Technological University New Delhi – 110042, India (E-mail: rajeshwaripandey@gmail.com)

Fig 2: OTRA Schematic Symbol

#### 2.0 Square root circuit

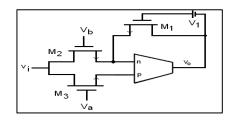

Square root structure based on OTRA is shown in Fig. 3. The MOSFET  $M_1$ operates in saturation region whereas  $M_2$ , and  $M_3$ operatein triode region. In triode region, the drain current through MOS transistor is given by:

$$I_D = K \frac{W}{L} \left( (V_{GS} - V_T) - \frac{V_{DS}}{2} \right) V_{DS}$$

... (2)

And the drain current in saturation region is given by:

$$I_D = \frac{K}{2} \frac{W}{L} (V_{GS} - V_T)^2 \dots (3)$$

where K, W and L respectively represent the transconductance, the width and the length of the MOSFET channel.

Using (2) and (3) the currents through inverting  $(I_n)$  and non-inverting  $(I_p)$  terminal of the OTRA can respectively be given as

$$I_{n} = K \left(\frac{W}{L}\right)_{2,3} \left( (V_{b} - V_{T})V_{i} - \frac{1}{2}V_{i}^{2} \right) + \frac{K}{2} \left(\frac{W}{L}\right)_{1} \left( (V_{o} + V_{1}) - V_{T} \right)^{2} \dots (4)$$

$$I_{p} = K \left(\frac{W}{L}\right)_{2,3} \left( (V_{a} - V_{T}) V_{i} - \frac{1}{2} V_{i}^{2} \right) \dots (5)$$

As  $R_m$  approaches infinity, current through inverting (I<sub>n</sub>) and non-inverting (I<sub>p</sub>) terminal of the OTRA tendto be equal. Thus, equating (4) and (5) results in

$$K\left(\frac{W}{L}\right)_{2,3}\left((V_a - V_T)V_i - \frac{1}{2}{V_i}^2\right) = K\left(\frac{W}{L}\right)_{2,3}\left((V_b - V_T)V_i - \frac{1}{2}{V_i}^2\right) + \frac{K}{2}\left(\frac{W}{L}\right)_1\left((V_o + V_1) - V_T\right)^2 \dots (6)$$

If V<sub>1</sub> is chosen such that V<sub>1</sub> = V<sub>T</sub>

$$V_O = \sqrt{\frac{2V_i \left(\frac{W}{L}\right)_{2,3} (V_a - V_b)}{\left(\frac{W}{L}\right)_1}}$$

$V_o = A \sqrt{V_i}$

Where

$$A = \sqrt{\frac{2\left(\frac{W}{L}\right)_{2,3}(V_a - V_b)}{\left(\frac{W}{L}\right)_1}}$$

The proposed square root circuit does not use any passive component and hence consumes less chip area. Therefore, this circuit is also suitable for integration.

## Fig 3: Square Root Circuit Using MOS Transistors

## **3.0 Simulation Results**

The proposed circuit for square root is verified through PSPICE simulation program using 0.18  $\mu$ m CMOS process parameters. The dual supply voltage for OTRA is 1.5V. The MOS transistors aspect ratios used in OTRA are given in Table 1. The transistors M<sub>2</sub> and M<sub>3</sub> have aspect ratio of 5 (W/L = 5 $\mu$ m/1 $\mu$ m). Transistor M1 has aspect ratio of 1 (W/L = 1 $\mu$ m/1 $\mu$ m). Voltages Va, V<sub>b</sub> and V<sub>1</sub> are chosen to be 1.05V, 1V and 0.4V respectively.

| Table I: MOS Transistors A | Aspect Ratios for OTRA |

|----------------------------|------------------------|

|----------------------------|------------------------|

| Transistor                            | W(μm)/L(μM) |

|---------------------------------------|-------------|

| M <sub>01</sub> -M <sub>03</sub>      | 100/2.5     |

| $\mathbf{M}_{04}$ , $\mathbf{M}_{07}$ | 10/2.5      |

| $M_{05}$ , $M_{06}$                   | 30/2.5      |

| M <sub>08</sub> - M <sub>011</sub>    | 50/2.5      |

| M <sub>012</sub> ,M <sub>013</sub>    | 100/2.5     |

| M <sub>014</sub>                      | 50/2.5      |

### **3.1 Dc characteristics**

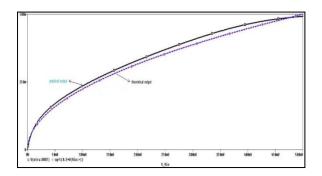

The DC Characteristics of the proposed analog Square root circuit are analyzed. The input Voltage Vi is swept from 0mV to 500mV in steps of 1mV. The curve between output (Vo) and input (Vi) voltages is plotted and is shown in Fig. 4. It is observed that the output voltage closely follows the square root of input voltage.

Fig 4: Simulation Result - V<sub>0</sub> vs V<sub>in</sub>

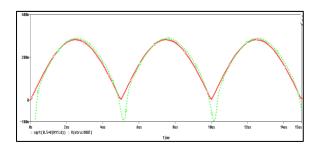

Fig 5: Transient Response

Fig 6: Frequency Spectrum

#### **3.2.Transient characteristics**

The Transient Characteristics of the proposed analog Square root circuit are analyzed.A squared sinusoidal voltage of frequency 100kHz and amplitude 400mV is given as input. The output

voltage (Vo) as well as expected output is plotted with respect to time and is shown in Fig. 5.The Frequency Spectrum of the proposed circuit is also analysed from 0Hz to 500KHz and is shown in fig 6.

The practical result matches the theoretical result.

### 4.0 Conclusions

A Low Voltage Analog Square Root circuit is proposed and verified using PSPICE. The circuit is made without using any passive elements and hence can be easily fabricated. The proposed circuit works for all input voltages less than 500mV. The Square Root circuit can be used in measurements and instrumentation and for various other purposes. With the added benefits of OTRA as stated previously, this structure overcomes the limitations of Voltage mode circuits like OPAMP.

### References

- [1] SParsnejad, Y Hu, H. Wan, E Ashoori, AJ Mason. Wide dynamic range multi-channel electrochemical instrument for in-field measurements, IEEE Sensors2016

- [2] A Hyogo, Y Fukutomi, K Sekine. Low Voltage Four-Quadrant Analog Multiplier Using Square-Root Circuit Based On Cmos Pair, IEEE International Symposium on Circuits and Systems, 1999

- [3] K Kimura. A Design Technique for an MOS Linear Transconductance Amplifier Consisting of a Source-Coupled Pair and Square-Root Circuits, The 10th Karuizawa Work- shop on Circuits and Systems (Japan), 1997, 25-29,

- [4] IM Filanovsky, HP Baltes. Simple CMOS analog square-rooting and squaring circuits, IEEE Transactions on Circuits and Systems, 39(4).

- [5] IY Fukutomi, A Hyogo, K Sekine. A New Square- Root Circuit and Its Application to a Source-Coupled Pair, Proceedings of NOLTA'98, 2, 1998, 555-558

- 32 International Journal of Advance Research and Innovation, Vol 5(4), Oct-Dec 2017

- [6] KNSalamaand, AMSoliman. CMOS operational transresistance amplifier for analog signal processing, Microelectronics Journal, 30(3), 1999, 235–245

- [7] R Pandey, N Pandey, BSriram, SK Paul. Single OTRA Based Analog Multiplier and Its Applications, International Scholarly Research Network ISRN Electronics, Article ID 890615, 2012,

- [8] H Mostafa, AM Soliman. A modified CMOS realization of the operational transresistance amplifier (OTRA). Frequenz, 60(3-4), 2006, 70–76