# Article Info

Received: 17 Jan 2020 | Revised Submission: 20 May 2020 | Accepted: 28 May 2020 | Available Online: 15 Jun 2020

# Performance of Different Full Adder Structures for Optimized Design

K. Rajasekhar\*, B. Sandhya\*, G. Srinivas\*\*, N. Manogna\* and K. Srinu\*

# ABSTRACT

Design of high performance and energy efficient digital systems are one of the most important research areas in VLSI system design which is suitable for real-time applications. One of the functional elements used in complex arithmetic circuits is an adder. To design an energy efficient adder one-bit full adder cell is designed based on adiabatic logic. The proposed ALFA cell is designed using adiabatic logic which results with the negligible amount of exchange of energy with the surrounding environment. Therefore, the application circuits based on this logic will have negligible energy loss due to heat dissipation. It requires 24 transistors to get the true and complimentary arithmetic sum and carry output. The proposed adiabatic logic based full adder (ALFA) cell processes the three single bit inputs and provides the output as sum, carry, sum bar and carry bar in a single architecture. The proposed ALFA cell reduces the power consumption by 98.49%, 90.93%, and 89.37%, respectively, when compared to CMOS full adder, 14T pass-transistor logic (PTL) with transmission gate (TG) full adder and 16T PTL with TG full adder.

Keywords: Pass transistor logic; Transmission gate; Adiabatic logic; CMOS logic.

#### **1.0 Introduction**

VLSI technology facilitates the designers for embedding more than hundred thousand of gates in a single IC. Achieving power reduction in full adder circuits is essential in handheld and portableVLSI based application circuits. Most of these application circuits incorporate processor-based blocks. Most probably, the circuits inside these blocks have full adder as their main element. Hence, in order to obtain the overall power optimization in a VLSI IC, as an initial attempt, the power reduction in full adders is the prime aim of the VLSI designers. Thus, in order to have an efficient approach, that is to implement the application circuits inside the VLSI. IC provide many choices for describing, synthesizing and verifying the designs with reduced complexity.Depletion of the silicon area during fabrication leads to the decline in power consumption. Thus, choosing low power consuming logic styles in the logical design stage and improving the efficiency of the physical design stage by adopting enhanced placement and routing techniques will yield a low power design with reduced propagation delay.

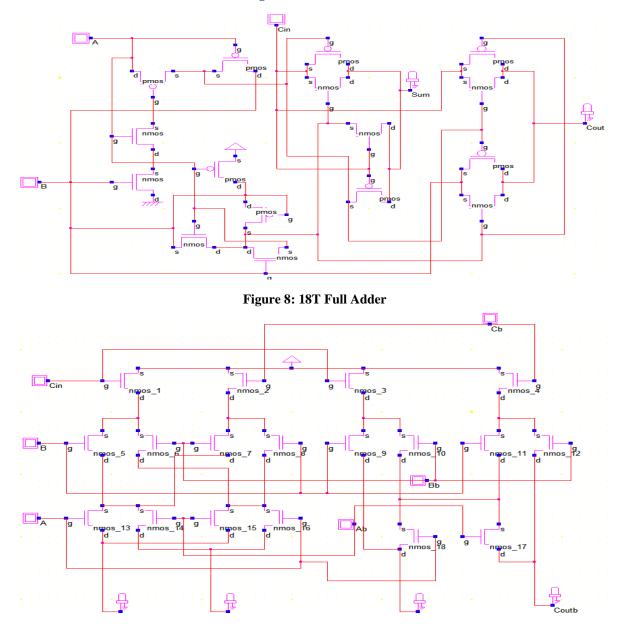

With this perception, the design and implementation of a low power full adder cell were carried out by selecting the low power consuming logic styles such as CMOS based 28T full adder cell, PTL based 16T full adder cell with TG, PTL based 14T full adder cell with TG and proposed ALFA cell. In VLSI, there is a trade-off between area, power and delay. To overcome these issues, it is necessary to design an optimized design. Hence the ALFA cell is proposed that overcomes the problems of the existing techniques such as CMOS Full Adder, PTL logic and transmission gate. The flow of this paper described full adder using various logic styles, elaborates the less area occupying and low power consuming efficient ALFA cell design approaches, the simulation outputs of the designed full adder cells with the considered logic styles are illustrated along with their respective area and power consumption results.

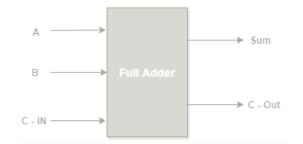

Full Adder is the adder which adds three inputs and produces two outputs. The first two inputs are A and B and the third input is an input carry as C-IN.

\*Department of Electronics and Communication Engineering, BITS, Vizag, Andhra Pradesh, India \*\*Corresponding author; Department of Electronics and Communication Engineering, BITS, Vizag, Andhra Pradesh, India (E-mail: gangumalla.jithendrakumar@gmail.com) The output carry is designated as C-OUT and the normal output is designated as S which is SUM. A full adder logic is designed in such a manner that can take eight inputs together to create a byte-wide adder and cascade the carry bit from one adder to the another.

Figure 1: Full Adder Truth Table

Logical Expression for SUM:

= A' B' C-IN + A' B C-IN' + A B' C-IN' + A B C-IN = C-IN (A' B' + A B) + C-IN' (A' B + A B') = C-IN XOR (A XOR B)= (1,2,4,7) Logical Expression for C-OUT: = A' B C-IN + A B' C-IN + A B C-IN' + A B C-IN = A B + B C - IN + A C - IN = (3,5,6,7)Another form in which C-OUT can be implemented: = A B + A C-IN + B C-IN (A + A')= A B C-IN + A B + A C-IN + A' B C-IN = A B (1 +C-IN) + A C-IN + A' B C-IN = A B + A C-IN + A' B C-IN= A B + A C-IN (B + B') + A' B C-IN = A B C-IN + A B + A B' C-IN + A' B C-IN = A B (C-IN + 1) + A B' C-IN + A' B C-IN = A B + A B' C-IN + A' B C-IN = AB + C - IN (A' B + A B')Therefore COUT = AB + C-IN (A EX - ORB)

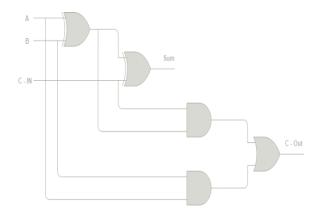

Figure 2: Full Adder Logic Circuit

Transmission gates are the fully restoring logic version of PTL whose output logic level does not degrade when passed through the respective logic level signal available on its inputs. Hence, in designing the full adder cells with PTL, in order to get the non- degraded outputs of the sum and carry, transmission gates are suitably inserted into the the the the the sum and carry.

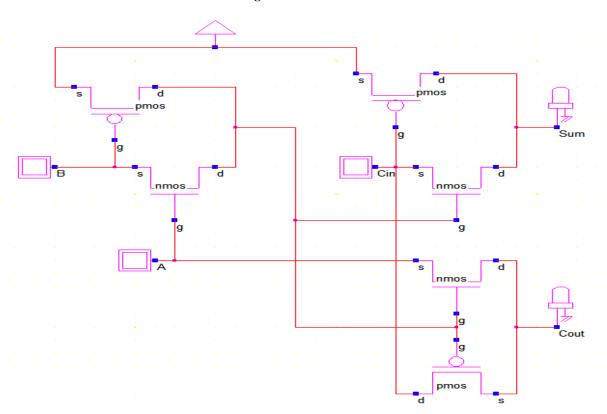

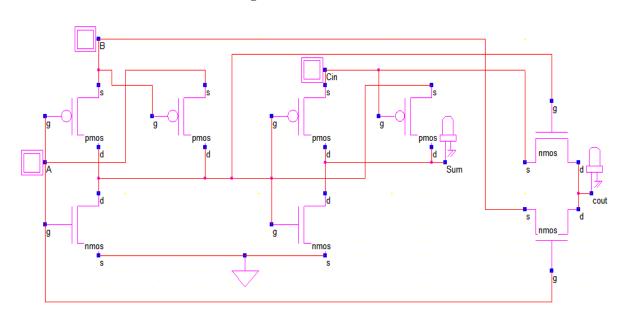

PTL with TG based 16 transistors full adder cell is shown inFig. 2.The simulation results show that the PTL with TG based16T full adder cell has lower power consumption than that of the CMOS based 28T full addercell. The PTL with TG based 14 transistors full adder cell is shown in Fig. 3.It has lower dynamic power consumption when compared

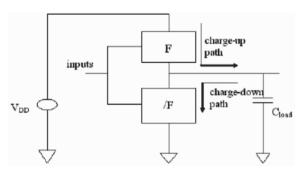

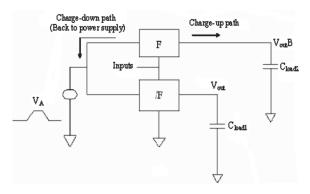

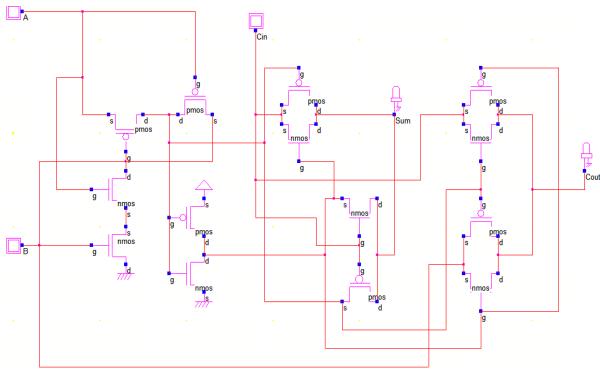

In this we will examine simple circuit configurations which can be used for adiabatic switching. A general circuit topology for the conventional CMOS gates and adiabatic counter parts is shown in Figure 3. To convert a conventional CMOS logic gate into an adiabatic gate, the pull-up transistor and the pull-down transistor networks must be replaced with complementary transmission-gate (T-gate). The T-gate network implementing the pullup function is used to drive the true output of the adiabatic gate. while the T-gate network implementing the pulldown function drives the complementary output node.

#### Figure 3: A Simple Adiabatic Logic Gate

Figure 4: 6T Full Adder

Figure 5: 8T Full Adder

Note that all the inputs should also be available in complementary form. Both the pull-up and pulldown networks in the adiabatic logic circuit are used for charging as well as discharging the output node capacitance, which ensures that the energy stored at the output node can be retrieved by the power supply, at the end of each cycle shown in Figure 4. To allow adiabatic operation, the DC voltage source of the original circuit must be replaced by a varying power supply with the ramped voltage output. Figure 6: 14T Full Adder

The necessary circuit modifications which are used to convert a conventional CMOS logic circuit into an adiabatic logic circuit increase the device count by a factor of two or even more.

#### 2.0 Adiabatic Logic Families

Adiabatic logic circuits classified into two types: (a) Quasi/ Partial Adiabatic Logic Circuits (b) Full Adiabatic Logic Circuits

- a) Quasi/Partial Adiabatic Logic Circuits: Quasi- adiabatic circuits have simple architecture and power clock system. The adiabatic loss occurs when current flows through non-ideal switch, which is proportional to the frequency of thepower-clock. Popular Partially Adiabatic families include the following:

- a. Efficient Charge Recovery Logic(ECRL).

- b. 2N-2N2P AdiabaticLogic.

- c. Positive Feedback Adiabatic Logic(PFAL).

- d. NMOS Energy Recovery Logic (NERL).

- e. Clocked Adiabatic Logic(CAL).

- f. True Single-Phase Adiabatic Logic (TSEL).

- g. Source-coupled Adiabatic Logic (SCAL).

### b) Full Adiabatic Logic Circuits:

Full-adiabatic circuits have no non-adiabatic

loss, but they are much more complex than quasi-adiabatic circuits. All the charge on the load capacitance is recovered by the power supply. Fully adiabatic circuits face a lot of problems with respect to the operating speed andtheinputspowerclocksynchronization.

Some Fully adiabatic logic families include:

- h. Pass Transistor Adiabatic Logic(PAL).

- i. Split-RailChargeRecoveryLogic(SCRL).

# 3.0 NMOS Energy Recovery Logic (NERL)

NMOS energy recovery logic (NERL), which uses NMOS transistors only and a simpler6-phase clocked power. Its area over head and energy consumption are smaller, compared with the other fully adiabatic logics. We employed bootstrapped NMOS switches to simplify the NERL circuits. With the simulation results for a full adder, we confirmed that the NERL circuit consumed substantially less energy than the other adiabatic logic circuits at lowspeed operation. NERL is more suitable than the other adiabatic logic circuits for the applications that do not require high performance but low energyconsumption. NMOS energy recovery logic gate.

Figure 7: 16T Full Adder

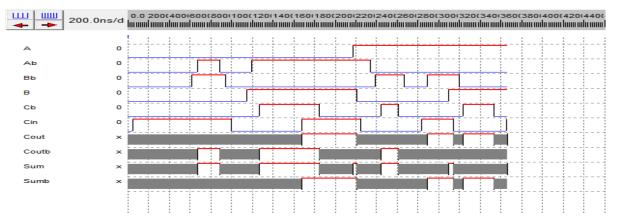

Figure 10: Layout for Proposed ALFA Cell

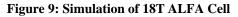

Fig illustrate the simulation output of the proposed ALFA cell. The outputs are represented as a sum, carryout. The layout design is carried out using the 90nmprocesswithapowersupplyvoltage of 1.2V. A6metallayer is utilized during the designprocess.

## 4.0 Conclusion

The ALFA cell has lower power consumption than that of the other versions of the full adder cell because of energy recycling. An ultra-power optimized ALFA cell is proposed using adiabatic logic with the aid of lower occupational area. The performance analysis of full adders in different logic styles is carried out with the focus on obtaining optimized power consumption

### References

- B Allahabad, A Al-Sheraida, A novel low power multiplexer-based full adder cell, in: IEEE Transactions, Florida Atlantic University, 2001, pp. 1433–1436, doi:10. 1109/ICECS.2001.957484.

- [2] S.D Kumar, H Thapliyal, A Mohammad, V Singh, K S Perumalla, Energy-efficient and

secure S-box circuit using symmetric pass gate adiabatic logic, in: IEEEComputer Society Annual Symposium on VLSI, USA, 2016, pp. 308–313, doi:10. 1109/ISVLSI.2016.45.

- [3] K Navi, O Kavehei, Low-power and highperformance1-Bit CMOS full-adder cell, J. Comput.3 (February (2)) (2008) 48– 54Iran10.1.1.128.8560.

- [4] D Wang, M Yang, W Cheng, X Guan, Z Zhu, Y Yang, Novel low power full adder cells in 180nm CMOS technology, in: 4th IEEE Conference on IndustrialElectronics and Applications, China, 2009, pp. 430–433, doi:10.1109/icie.2009. 5138242.

- [5] M Alioto, G Palumbo, NAND/NOR adiabatic gates: power consumption evaluate- tionand comparison versus the Fan-In, IEEE Trans. Circuits Syst.—I49 (Septem- ber (9)) (2002) 1253–1262,doi:10.1109/TCSI.2002.

- [6] S Goel, A Kumar, M A Bayoumi, Design of robust, energy-efficient full adders for deepsub micrometer design using Hybrid-CMOS logic style, IEEE Trans. Very Large ScaleInteger. (VLSI) Syst. 14 (December (12)) (2006) 1309–1321, doi:10.1109/ TVLSI.2006.887807.

- [7] G Heimskringla, P Lee, 16-bit clocked adiabatic logic (CAL) logarithmic signal processor, in: IEEE Transactions, University of Kent, 2012, pp. 113–116, doi:10. 1109/MWSCAS.2012.6291970.

- [8] C O Campos-Aguillón, R Celis-Cordova, I K Hänninen, C S Lent, A O Orlov, G L Snider, A Mini-MIPS microprocessor for adiabatic computing, in: IEEE Trans- actions, USA, 2016, pp. 1–7, doi: 10.1109/ICRC.2 016.7738678.

- [9] L Reddi, V Vivekananda, Implementation of full adder with 18-transistors using low power design, Int. J. Adv. Trends Eng. Sci. Technol. 3 (March (2)) (2018) 11– 14 India,doi:10.5121/ijitcs.2012.2602.

- [10] K N Mishra, Efficient carry generation technique incorporating energy recoverring logic circuitry for low power VLSI, in: IEEE Transactions, India, 2008, pp. 332–335,doi:10.1109/ECCSC.2008.4611703.

- [11] S A Marina, S Pradeepa T, A Rajeswari, Analysis of full adder using adiabatic charge recovery logic, in: International Conference on Circuit, Power and Com- putting Technologies, India, 2016, pp. 1–6, doi: 10.1109/ICCPCT.2016.7530184.

- [12] M Shoba, R Nakkeeran, GDI based full adders for energy efficient arithmetic applications, Eng. Sci. Technol. Int. J. (2016) 485–496 India, doi:10.1016/j.jestch. 2015.09.006.

- [13] S A Rahma, G Khanna, Performance metrics analysisof 4 bit array multiplier circuit using 2 pascl logic, in: IEEE Transactions, India, 2014, pp. 1–5, doi:10. 1109/icgccee.2014. 6922276.

- [14] H Ni, X Sheng, J Hu, Voltage scaling for adiabatic register file based on complementary pass transistor adiabatic logic, in: Future Inteligent Information Sys- tems, Chinna, 2011, pp. 39–46,doi:10.1007/978- 3-642-19702- 2\_6.

- [15] D Chaudhuri, A Nag, S Bose, Low power full adder circuit implemented in differentlogic, Int. J. Innovative Res. Sci. Eng. Technol. India (2014) 124–129.

- [16] Nazrul Anuar, Yasuhiro Takahashi, Toshikazu Sekine, Two phase clocked adiabatic static CMOS logic and its logic family, J. Semiconductor Technol. Sci. 10 (March (11)) (2010) 1–10 JapanT., Jones, M.: 'The title of the paper', IET Syst. Biol., 2007, 1, (2), pp. 1–7, doi:10.1007/978-981-10- 5828-53Smith.